# Laser directly written junctionless in-plane-gate neuron thin film transistors with AND logic function

Li Qiang Zhu, Guo Dong Wu, Ju Mei Zhou, Wei Dou, Hong Liang Zhang et al.

Citation: Appl. Phys. Lett. 102, 043501 (2013); doi: 10.1063/1.4789515

View online: http://dx.doi.org/10.1063/1.4789515

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v102/i4

Published by the American Institute of Physics.

#### **Related Articles**

Graphene on boron nitride microwave transistors driven by graphene nanoribbon back-gates Appl. Phys. Lett. 102, 033505 (2013)

Chaotic quantum transport near the charge neutrality point in inverted type-II InAs/GaSb field-effect transistors Appl. Phys. Lett. 102, 033504 (2013)

Gate traps inducing band-bending fluctuations on AlGaN/GaN heterojunction transistors Appl. Phys. Lett. 102, 023511 (2013)

Novel metal gates for high κ applications J. Appl. Phys. 113, 034107 (2013)

Organic field-effect transistor nonvolatile memories based on hybrid nano-floating-gate Appl. Phys. Lett. 102, 023303 (2013)

### Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

#### ADVERTISEMENT

## Laser directly written junctionless in-plane-gate neuron thin film transistors with AND logic function

Li Qiang Zhu, Guo Dong Wu, Ju Mei Zhou, Wei Dou, Hong Liang Zhang, and Qing Wan<sup>a)</sup> *Ningbo Institute of Materials Technology and Engineering, Chinese Academy of Sciences, Ningbo 315201, People's Republic of China*

(Received 4 July 2012; accepted 14 January 2013; published online 28 January 2013)

Junctionless oxide-based neuron thin-film transistors with in-plane-gate structure are fabricated at room temperature by a laser scribing process. The neuron transistors are composed of a bottom indium-tin-oxide floating gate and multiples of in-plane control gates. The control gates, coupling with the floating gate, control the "on" and "off" of the transistor. Effective field-effect modulation of the drain current has been realized. AND logic is demonstrated on a dual in-plane gate neuron transistor. The developed laser scribing technology is highly desirable in terms of the fabrication of high performance neuron transistors with low-cost. © 2013 American Institute of Physics. [http://dx.doi.org/10.1063/1.4789515]

Multigate devices have been proposed as a viable solution to complementary metal-oxide-semiconductor (CMOS) scaling issues. 1 More functions could be introduced in a single device through multi-independent gate, therefore increasing the functional density for a given area. Dual-gate thin-film transistors (TFTs) have attracted a lot of attentions in chemical and biological sensing, pixel display driver, and logic circuit applications.<sup>2-6</sup> A highly functional MOS transistor called neuron MOS transistor has been developed by executing a weighted sum calculation of multiple input signals and then controls the "on" and "off" states of the transistor, thus realizing the neuron function.<sup>7-9</sup> The device has a floating gate and multiple input control gates which are capacitively coupling with the floating gate, featuring a full compatibility with standard CMOS process. However, due to the multiple gate/dielectric deposition and precise photolithography steps, the fabricating of such neuron transistors by standard CMOS process is expensive and time-consuming. Recently, the concept of junctionless transistors has been proposed and explored. 10–12 Compared with the conventional field-effect transistors (FETs), the unique features of such junctionless transistors is that the channel doping is the same or comparable to that of the source and drain (S/D), therefore no sour/drain junction formation steps are needed, and the carrier transport is less sensitive to the channel interface. However, fabrication of these junctionless FETs is still rather challenging. As an interesting concept for promising functional devices, in-plane gate transistors have been developed as logic devices, <sup>13</sup> rectifier, <sup>14,15</sup> negative differential resistance devices, 16 etc. Laser scribing process was also proposed for source/drain patterning. 17,18 However, masks are still needed during the TFTs fabrication.

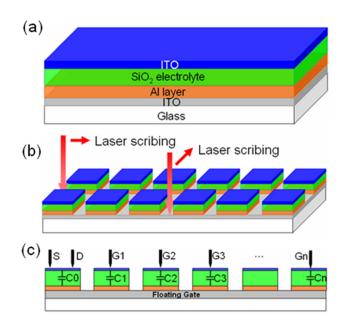

In this work, a laser scribing method without any masks and photolithography is developed to directly write the junctionless in-plane-gate neuron TFTs arrays on glass substrates at room temperature. SiO<sub>2</sub>-based solid electrolyte works as gate dielectrics. <sup>19,20</sup> The channel and source/drain electrodes

are realized by a thin indium-tin-oxide (ITO) layer without any intentional source/drain junction. The bottom ITO layer works as a floating gate, while the top isolated ITO works as the in-plane control gate. Effective field-effect modulation of the drain current has been realized on both the single in-plane-gate (SG) mode and the dual in-plane-gate (DG) mode. Good electrical performance has been exhibited on SG neuron TFT: low OFF current of  $<3\,\mathrm{pA}$ , high  $I_{\mathrm{on}}/I_{\mathrm{off}}$  ratio of  $>10^6$ , high electron mobility of  $\sim12.6\,\mathrm{cm}^2/\mathrm{Vs}$ , and low subthreshold swing of  $0.25\,\mathrm{V/dec}$ . AND logic was experimentally demonstrated on the DG neuron TFT. The developed laser scribing technology is highly desirable in terms of the low-cost fabrication process.

Fabrication of ITO junctionless in-plane gate neuron transistors was performed at room temperature, as schematically shown in Figs. 1(a) and 1(b). After cleaning the substrates, a 100-nm-thick Al thin film was deposited on ITO surface by sputtering. Then, a 2-µm-thick SiO<sub>2</sub>-based solid electrolyte film was deposited by plasma enhanced chemical vapor deposition (PECVD) using SiH<sub>4</sub> and O<sub>2</sub> as reactive gases. Finally, a 25-nm-thick ITO films were deposited on the SiO<sub>2</sub>-electrolyte based gate dielectrics by sputtering. The ratio frequency (RF) power, Ar flow rate, and the chamber pressure were set to be 100 W, 14 sccm, and 0.5 Pa, respectively. Then, the neuron TFTs were fabricated on the prepared stacks of ITO/SiO<sub>2</sub>-electrolyte/Al/ITO/glass substrates by adopting a laser scribing process. The focused laser beam selectively etches out the deposited thin films due to a localized thermoelastic force caused by rapid thermal expansion resulting from the pulsed laser irradiation. The laser patterned ITO arrays are with the dimension of  $1 \text{ mm} \times 0.2 \text{ mm}$ . The capacitors (C1, C2, C3,..., Cn) are effectively coupled through bottom ITO floating gate, as shown in Fig. 1(c). The source and drain are obtained on the same ITO region, while the isolated ITO region works as the in-plane control gate. When set signals on G1 (or G1 and G2), the junctionless SG (or DG) neuron TFT is obtained. The capacitance-frequency measurement of the SiO<sub>2</sub>-based solid electrolyte was performed using an impedance analyzer. The electrical characteristics of the junctionless SG and DG TFTs were measured

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: wanqing@nimte.ac.cn.

FIG. 1. (a) The obtained ITO/SiO $_2$ -electrolyte/Al/ITO/Glass stack. (b) Laser scribing process results in the isolation of the top ITO films as well as the SiO $_2$ -electrolyte and Al layer. (c) Schematic cross-sectional view of the laser patterned junctionless in-plane gate neuron TFTs structure. The capacitors (C1, C2, C3,..., Cn) are effectively coupled through bottom ITO floating gate.

with a Keithley 4200 SCS semiconductor parameter analyzer at room temperature in the dark.

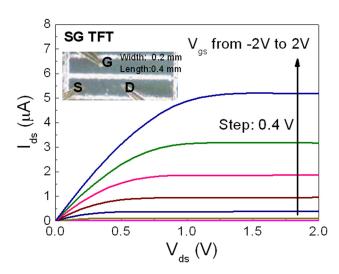

The output characteristics of the laser patterned junctionless SG neuron TFTs are shown in Fig. 2. The nominal channel length is 0.4 mm, while the channel width is 0.2 mm (as shown in the inset of Fig. 2). At low  $V_{\rm ds}$ , the drain current increases linearly with drain voltage, indicating that the device has a good ohmic contact. At the higher  $V_{\rm ds}$ , the drain current gradually approaches a saturated value. With a gate voltage of 2 V, the saturation current is observed to be  ${\sim}5~\mu{\rm A}$  at a drain voltage of 2 V.

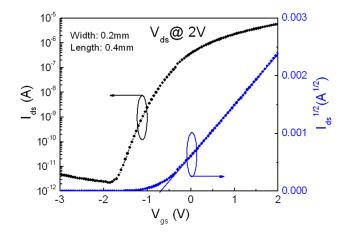

Fig. 3 shows the transfer characteristics of the junctionless SG neuron TFTs at saturation mode, fixed at  $V_{\rm ds}$  of 2 V. It can be found that  $I_{\rm ds}$  can be effectively modulated by  $V_{\rm gs}$ .

FIG. 2. Output characteristics ( $I_{ds}$  vs  $V_{ds}$ ) of the laser patterned junctionless SG TFTs. Inset: Top view optical image of the junctionless SG neuron TFTs in electrical measurement on a probe station.

FIG. 3. Transfer characteristics ( $I_{ds}$  vs  $V_{gs}$  and the square root of  $I_{ds}$  vs  $V_{gs}$ ) of the junctionless SG neuron TFTs at saturation mode, fixed at  $V_{ds}$  of 2 V.

The subthreshold swing (S) is found to be  $\sim 0.25 \, \text{V/dec}$ . The drain current on/off ratio  $I_{\text{on}}/I_{\text{off}}$  is determined to be  $\sim 3 \times 10^6$ . A threshold voltage  $V_{\text{th}}$  of  $-0.7 \, \text{V}$  is estimated by extrapolating the linear portion of the curves relating  $I_{\text{ds}}^{1/2}$  and  $V_{\text{gs}}$  to  $I_{\text{ds}}^{1/2} = 0$ . The field-effect mobility ( $\mu$ ) in the saturation region can be extracted from the following equation:

$$I_{ds} = \left(\frac{WC_{i}\mu}{2L}\right)(V_{gs} - V_{th})^{2} \quad (V_{ds} > V_{gs} - V_{th}), \quad (1)$$

where L is the channel length, W is the channel width, and  $C_i$  is the unit area capacitance of the dielectrics. Capacitor of  $SiO_2$ -based solid electrolyte with two in-plane ITO electrodes was measured using an ITO/SiO $_2$ -electrolyte/Al/ITO in-plane test structure as shown in Fig. 1(c) with G1 and S as the electrode (results not shown here). The in-plane gate capacitance of  $0.25\,\mu\text{F/cm}^2$  is used to calculate the field-effect mobility. The field-effect electron mobility is estimated to be  $\sim 12.6\,\text{cm}^2/\text{Vs}$ .

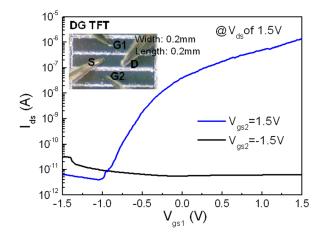

Fig. 4 shows the transfer characteristics of the junctionless DG neuron TFTs at saturation region, fixed at  $V_{\rm ds}$  of 1.5 V. Both the channel width and the channel length is  $\sim$ 0.2 mm (as shown in the inset of Fig. 4). The drain currents are controlled by two gates (G1 and G2). G1 bias sweeps

FIG. 4. The transfer characteristics of the junctionless DG neuron TFTs at saturation region, fixed at  $V_{\rm ds}$  of 1.5 V. Inset: Top view optical image of the junctionless DG neuron TFTs in electrical measurement on a probe station.

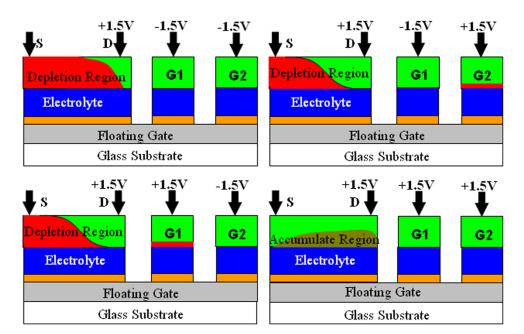

FIG. 5. Schematic images of the dual in-plane control gate ITO neuron TFT showing the depletion regions (in red) formed under different biases, illustrating AND logic.

from -1.5 V to 1.5 V with the fixed G2 bias set to 1.5 V and  $-1.5 \,\mathrm{V}$ , respectively. It could be found obviously from Fig. 4 that the drain current could be effectively modulated by G1 bias with fixed G2 bias of 1.5 V. The drain current can be turned on or off effectively with the drain current on/off ratio  $I_{on}/I_{off}$  of above  $10^5$ . The subthreshold swing (S) and the threshold voltage ( $V_{th}$ ) are found to be  $\sim 0.25 \text{ V/dec}$  and -0.25 V, respectively. On the other hand, the drain current cannot be turned on effectively under G2 bias of  $-1.5 \,\mathrm{V}$ . The drain current is controlled by depletion region created by the two control gates as shown in Fig. 5. For example, when G2 is negative biased at -1.5 V, electrons in the ITO channel will be depleted, resulting in a low OFF drain current. At the same time, since G1 is also ITO film with same thickness as the channel, it would also be depleted. Then, the value of gate capacitance would be decreased due to the depletion capacitor in series, and the electrostatic coupling ability of G1 decreases. So such TFTs cannot be turned on by G1 when G2 is biased -1.5 V. While when both the control gates are biased +1.5 V, the ITO channel works in accumulate region, resulting in a high ON current. Such DG neuron TFT performances are meaningful for logic gate applications.

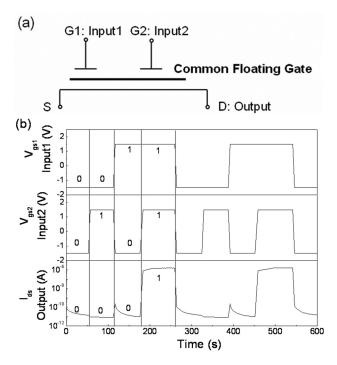

The logic circuit of a DG neuron TFT is shown in Fig. 6(a). The devices are characterized by applying different fixed potentials, corresponding to two logic states, HIGH state ("1") at 1.5 V and LOW state ("0") at -1.5 V, input directly and independently to each of the two control gates (see the logic circuit diagram for input 1 and input 2). This in-plane gate logic operates as an AND gate as demonstrated in Fig. 6(b). The drain current monitored are also detected as output ("1":  $I_{ds}$  above 0.1  $\mu$ A; or "0":  $I_{ds}$  below 0.01  $\mu$ A). At "00," "01," or "10," the device is in the OFF state. A low OFF current of <0.01 nA is measured. For state "11," the device is ON with a HIGH current of  $>0.7 \mu A$ . The results indicate a high ON/OFF ratio of  $\sim 10^4$  between the two logic states. Though there are some small noises of below 0.1 nA, the HIGH/LOW ratio output is still over 10<sup>3</sup>. The HIGH/ LOW ratio is high enough for reliable logic operations.

In summary, a simple laser scribing process without any mask and photolithography is implemented in fabricating junctionless in-plane gate neuron TFT arrays. Such junctionless neuron TFTs feature that the channel and the source/drain electrodes are of the same ITO films without any intentional source/drain junction formation steps. The bottom ITO layer works as a floating gate, while the top isolated ITO works as the in-plane control gate. The control gates, coupling with the floating gate, control the "on" and "off" of the transistor. Effective field-effect modulation of the drain current has been realized on both the SG mode and the DG mode. AND logic is demonstrated on a dual in-plane gate neuron transistor with a high HIGH/LOW ratio, allowing the reliable logic operation. The developed laser scribing

FIG. 6. (a) Logic circuit diagram of the DG neuron TFT. (b) AND logic operation.

technology is highly desirable in terms of the fabrication of high performance neuron transistors with low costs.

The authors are grateful for the financial supports from the National Program on Key Basic Research Project (2012CB933004) and the National Natural Science Foundation of China (11174300 and 11104288).

- <sup>8</sup>B. C. Jacquot, C. Lee, Y. N. Shen, and E. C. Kan, IEEE Sens. J. 7, 1429 (2007)

- <sup>9</sup>P. J. Wang, J. G. Lu, and J. Xu, Neural Comput. Appl. **17**, 139 (2008).

- <sup>10</sup>C. W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J. P. Colinge, Appl. Phys. Lett. **94**, 053511 (2009).

- <sup>11</sup>J. P. Colinge, C. W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A. M. Kelleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. 5, 225 (2010).

- <sup>12</sup>C.-J. Su, T.-I. Tsai, Y.-L. Liou, Z.-M. Lin, H.-C. Lin, and T.-S. Chao, IEEE Electron Device Lett. **32**, 521 (2011).

- <sup>13</sup>Y. Komatsuzaki, K. Saba, K. Onomitsu, H. Yamaguchi, and Y. Horikoshi, Appl. Phys. Lett. **99**, 242106 (2011).

- <sup>14</sup>T. Muller, A. Lorke, Q. T. Do, F. J. Tegude, D. Schuh, and W. Wegscheider, Solid-State Electron. 49, 1990 (2005).

- <sup>15</sup>M. J. Thornton, B. Ketelaars, E. V. D. Heuve, H. Roosen, S. Smout, and M. Losad, Appl. Phys. Lett. 99, 173301 (2011).

- <sup>16</sup>Y. Komatsuzaki, K. Higashi, T. Kyougoku, K. Onomitsu, and Y. Hori-koshi, Phys. Status Solidi C 8, 408 (2011).

- <sup>17</sup>H. Shin, B. Sim, and M. Lee, Opt. Lasers Eng. 48, 816 (2010).

- <sup>18</sup>H. Lee, H. Shin, Y. Jeong, J. Moon, and M. Lee, Appl. Phys. Lett. 95, 071104 (2009).

- <sup>19</sup>J. Jiang, J. Sun, L. Q. Zhu, G. D. Wu, and Q. Wan, Appl. Phys. Lett. 99, 113504 (2011).

- <sup>20</sup>J. Jiang, J. Sun, W. Dou, and Q. Wan, IEEE Electron Device Lett. 33, 65 (2012).

<sup>&</sup>lt;sup>1</sup>J. P. Colinge, *FinFETs and Other Multi-Gate Transistors* (Springer, New York, 2008), pp. 1–48.

<sup>&</sup>lt;sup>2</sup>Y. M. Park and A. Salleo, Appl. Phys. Lett. **95**, 133307 (2009).

<sup>&</sup>lt;sup>3</sup>M. Spijkman, J. J. Brondijk, T. C. T. Geuns, E. C. P. Smits, T. Cramer, F. Zerbetto, P. Stoliar, F. Biscarini, P. W. M. Blom, and de D. M. Leeuw, Adv. Funct. Mater. **20**, 898–905 (2010).

<sup>&</sup>lt;sup>4</sup>M. Spijkman, E. C. P. Smits, J. F. M. Cillessen, F. Biscarini, P. W. M. Blom, and D. M. de Leeuw, Appl. Phys. Lett. **98**, 043502 (2011).

<sup>&</sup>lt;sup>5</sup>C. H. Park, K. H. Lee, M. S. Oh, K. Lee, S. Im, B. H. Lee, and M. M. Sung, IEEE Electron Device Lett. **30**, 30 (2009).

<sup>&</sup>lt;sup>6</sup>M. Spijkman, K. Myny, E. C. P. Smits, P. Heremans, P. W. M. Blom, and D. M. de Leeuw, Adv. Mater. 23, 3231 (2011).

<sup>&</sup>lt;sup>7</sup>T. Shibata and T. Ohmi, IEEE Trans. Electron Devices **39**, 1444 (1992).