# Threshold voltage tuning in a-IGZO TFTs with ultrathin SnO<sub>x</sub> capping layer and application to Depletion-Load Inverter

Mei Wang, Lingyan Liang, Hao Luo, Shengnan Zhang, Hongliang Zhang, Kashif Javaid, and Hongtao Cao

Abstract—Tunable threshold voltage of a thin-film transistor (TFT) is highly desirable for designing multifunctional electronic circuits. In this work, an ultrathin  $SnO_x$  capping layer was adopted to modify the threshold voltage of bottom-gate amorphous indium-gallium-zinc-oxide (a-IGZO) TFTs. A threshold voltage shift from 15.2 to -9.0 V was observed as the  $SnO_x$  thicknesses increased from 0 to 19 nm, accompanying by a sizable increase of the intrinsic electron concentration in the channel layer. It was believed that the  $SnO_x$  capping layer can extract loosely bound oxygen from the a-IGZO, which was supported by the  $SnO_x$  composition variation with its thickness. Combining an uncovered a-IGZO TFT with a  $SnO_x$  capped a-IGZO TFT, an Enhancement/Depletion inverter with a voltage gain up to 45.9 was successfully demonstrated.

Index Terms—Amorphous indium-gallium-zinc-oxide (a-IGZO), Tin oxides  $(SnO_x)$ , thin-film transistor, inverter, capping layer.

# I. INTRODUCTION

morphous indium-gallium-zinc-oxide thin film transistor A (a-IGZO TFT) arrays have attracted ever-increasing attention as backplanes in active matrix liquid crystal displays (AMLCDs) or active-matrix organic light-emitting diode displays (AMOLEDs) [1]. Meanwhile, there have been various attempts to use a-IGZO TFTs in logic circuits [2], photodetectors [3], memory devices [4], bio-sensors [5] and so on. Oxide-based inverters, acting as "built blocks" of logic extensively studied in recent years. Complementary inverters using p-type SnO<sub>x</sub>/n-type In<sub>2</sub>O<sub>3</sub> [6] n-type IGZO/p-type pentacene hybrid complementary-like inverters based on ambipolar SnO TFTs [8], resistor-loaded inverters, and enhancement/depletion (E/D) inverters have already been demonstrated. Among them, the E/D inverter utilizing two n-channel TFTs with different threshold voltage  $(V_{th})$  is a promising supplementary technology for complementary logic circuits.

In order to tune the  $V_{\rm th}$  difference as much as possible, various methods have been reported, such as varying the active layer thickness [9], adopting distinct active layer material [10], selectively inducing the negative bias illumination temperature stress (NBITS) to the load TFT [11], and applying a constant

This work is supported by the National Natural Science Foundation of China (Grant No. 61474126), and National Basic Research Program of China (2012CB933003).

M. Wang, L. Y. Liang, H. Luo, S. N. Zhang, H. L. Zhang, K. Javaid and H. T. Cao are with Ningbo Institute of Material Technology and Engineering, Chinese Academy of Sciences, & Key Laboratory of Additive Manufacturing Materials of Zhejiang Province, Ningbo 315201, People's Republic of China. (E-mail: h\_cao@nimte.ac.cn; lly@nimte.ac.cn).

K. Javaid is also with the Department of Physics, GC University Faisalabad, Allama Iqbal Road, 38000 Faisalabad, Pakistan.

positive bias on the top gate [12], etc. However, these inverters demonstrated either low voltage gains (< 40) or rather complicated fabrication processes, limiting their applications.

1

Passivation layers with a thickness larger than 100 nm were generally deposited to improve the electrical stability of TFTs. However, various passivation layers (such as  $SiO_x$  [13], MgF<sub>2</sub> [14]) fabricated in vacuum system were found to not only shift the  $V_{th}$  negatively but also induce a very large off-current. In this letter, by introducing a thin  $SnO_x$  capping layer onto the uncovered back channel surface (Bottom-gate top-contact TFT structure), tunable  $V_{th}$  of a-IGZO TFTs was achieved without scarifying other device properties. Then an E/D inverter with a voltage gain up to 45.9 was constructed by connecting an uncovered a-IGZO TFT with a  $SnO_x$ -covered one. This E/D inverter has a relatively simple fabrication process, manifesting a good application potential for the future logic circuits based on oxide semiconductors.

# II. DEVICE STRUCTURE AND FABRICATION

Bottom-gate transistors using a-IGZO as the channel layer were fabricated at room temperature. A-IGZO thin films were deposited on SiO<sub>2</sub> (100 nm)/Si substrate by RF sputtering, applying a 2 in. IGZO target (1:1:1 mol. % of In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>: ZnO) at a power of 80 W. The base pressure of the chamber was less than  $4 \times 10^{-4}$  Pa. 30 nm channel films were deposited in a 100% Ar atmosphere at a constant pressure of 0.21 pa (Ar flow = 6 sccm). Afterwards, a shadow mask was used to define the channel length and width of 400 and 800 µm, respectively. Ti/Au (30 nm/30 nm) source/ drain electrodes were deposited by electron beam evaporation using the second shadow mask. The devices were then annealed at 250 °C in the air for 1 hour. Amorphous SnO<sub>x</sub> films with different thicknesses were deposited at room temperature onto the back channel surface of the fabricated a-IGZO TFTs through electron beam evaporation (Deposition details were reported elsewhere [15]). Finally, an E/D inverter was fabricated by connecting a bare TFT as the driver and an 8.5 nm SnO<sub>x</sub>-covered TFT as the load. The fabricated TFTs and inverters are finally passivated by SU-8 photo-resist to improve the device stability.

## III. RESULTS AND DISCUSSION

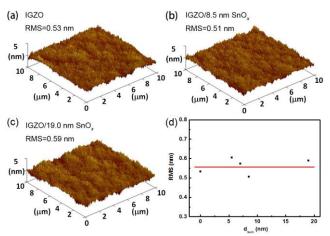

Surface morphologies of the a-IGZO films covered with or without amorphous  $SnO_x$  films were investigated using atomic force microscope (AFM), as seen in Figure 1. These surfaces are apparently smooth without obvious embossment. As shown in figure 1(d), the root mean square (RMS) roughness as a function of the  $SnO_x$  thickness is ranging from 0.50-0.60 nm, indicating that the deposition of the  $SnO_x$

Fig. 1. (a), (b) and (c) AFM images of the a-IGZO films covered with 0, 8.5 and 19.0 nm  $SnO_x$ . (d) The RMS values vs.  $SnO_x$  thicknesses .

capping layer has a marginal influence on the surface morphology of the a-IGZO surface.

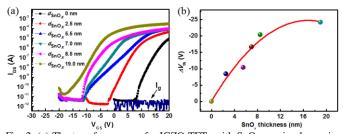

The electrical properties of the devices were obtained at room temperature in the dark using a semiconductor parameter analyzer. Figure 2(a) shows the transfer characteristics of the TFTs with varied  $SnO_x$  thicknesses ( $d_{SnOx}$ ), and the main electrical parameters are summarized in Table 1. The uncovered TFT shows a positive turn-on voltage  $(V_{on})$  and  $V_{th}$ , indicating that the TFT works in an enhancement mode. Interestingly, the introduction of SnO<sub>x</sub> capping layer triggers the conversion from the enhancement mode to depletion one. As  $d_{SnOx}$  increases from 0 to 19 nm, the  $V_{on}$  changes from 8.0 to -18.0 V, while the  $V_{\rm th}$  shifts from 15.2 to -9.0 V. The negative-shift of both  $V_{\rm on}$  and  $V_{\rm th}$  implies that the intrinsic electron concentration in the channel layer increases as  $d_{SnOx}$ , which is confirmed by the Hall-effect measurement. Both the bare a-IGZO film and SnO<sub>x</sub> capped a-IGZO film with  $d_{SnOx}$ =2.5 nm have high resistivity beyond the limitation of the Hall measurement. The films with  $d_{SnOx} = 5.5-8.5$  nm show electron concentrations around  $10^{16}$ - $10^{17}$  cm<sup>-3</sup>. When  $d_{SnOx}$  is up to 19 nm, the film has an electron concentration up to  $2.7 \times 10^{18}$  cm<sup>-3</sup>, leading to relatively high off and on currents of the corresponding TFT. As a result, the carrier concentration variation-induced tunable  $V_{th}$  of a-IGZO TFTs was achieved in this study, which facilitates us to construct E/D inverters. Additionally, It should be noted that the TFTs with  $d_{SnOx} = 5.5$ & 7.0 nm show a clear subthreshold hump in the transfer curves, substantially increasing the subthreshold slope (S.S). At  $d_{SnOx}$  = 8.5 nm, however, the subthreshold hump almost disappears. With further increasing  $d_{SnOx}$ , the S.S rebounds back due to the high intrinsic electron concentration. In this case, it is difficult for the voltage to switch the device on and off quickly.

Figure 2(b) shows the variation in  $V_{\rm th}$  shift ( $\Delta V_{\rm th}$ ) as a function of  $d_{SnOx}$ . The devices present more dramatic increase in  $\Delta V_{\rm th}$  in the range of  $d_{SnOx} \leq 8.5$  nm. With further increasing  $d_{SnOx}$ , the rate of increment gradually slows down. These results exhibit a strong dependence of  $\Delta V_{\rm th}$  on  $d_{SnOx}$ , meaning that the shift is highly related to the capping layer property (such as surface morphology and chemical composition, etc.). The AFM results have demonstrated that the film surface morphologies show small changes with  $d_{SnOx}$ . Next, the SnO<sub>x</sub> chemical component variations of the capping layer with its thickness will be further investigated to clarify the origin of the  $V_{\rm th}$  shift.

Fig. 2. (a) The transfer curves of a-IGZO TFTs with SnO<sub>x</sub> capping layers in different thicknesses,  $V_{\rm DS}$ =10 V. (b) The dependence of  $\Delta V_{\rm th}$  on  $d_{SnO_{\rm X}}$ , and  $\Delta V_{\rm th} = V_{\rm th} \ (d_{SnO_{\rm X}} \neq 0)$  -  $V_{\rm th} \ (d_{SnO_{\rm X}} = 0)$ .

TABLE I ELECTRICAL PARAMETERS OF A-IGZO TFTS WITH OR WITHOUT SNO  $_{\rm x}$  CAPPING LAYERS

| d <sub>SnOx</sub> (nm) | V <sub>on</sub> (V) | V <sub>th</sub> (V) | $\mu_{FE}$ (cm <sup>2</sup> /Vs) | S.S<br>(V/decade) | I <sub>on/off</sub><br>ratio |

|------------------------|---------------------|---------------------|----------------------------------|-------------------|------------------------------|

| 0                      | 8.0                 | 15.2                | 9.59                             | 0.707             | 2.3×10 <sup>6</sup>          |

| 2.5                    | -2.3                | 6.8                 | 10.06                            | 1.220             | $2.0 \times 10^{7}$          |

| 5.5                    | -11.1               | 4.8                 | 11.16                            | 1.333             | $1.9 \times 10^{7}$          |

| 7.0                    | -11.1               | -1.5                | 9.55                             | 0.672             | $1.9 \times 10^{7}$          |

| 8.5                    | -11.8               | -5.2                | 10.34                            | 0.475             | $1.9 \times 10^{7}$          |

| 19.0                   | -18.0               | -9.0                | 15.00                            | 1.177             | $1.7 \times 10^7$            |

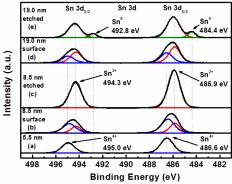

X-ray photoelectron spectroscopy (XPS) was performed to analyze the chemical states of the  $SnO_x$  capping layers. The binding energy data were calibrated with respect to the C 1s signal of ambient hydrocarbons (C-H and C-C) centered at 284.8 eV. To obtain the depth-profile chemical composition of the  $SnO_x$ , high dose of argon ions (Ion energy of 2 KeV, current density of 5  $\mu$ A/cm² roughly) were utilized to sputter away the top surface layer of  $SnO_x$ .

At  $d_{SnOx} = 5.5$  nm, the elemental information of both the SnO<sub>x</sub> capping layer and the a-IGZO underlayer was detected, so no Ar<sup>+</sup> ion etching process was carried out in this case. The Sn 3d spectrum of the 5.5 nm SnO<sub>x</sub> shown in figure 3(a) depicts a spin-orbit doublet peak located at 486.6 eV (Sn<sup>4+</sup> 3d<sub>5/2</sub>) and 495.0 eV (Sn<sup>4+</sup> 3d<sub>3/2</sub>), matching very well with those reported for SnO<sub>2</sub> [16]. This indicates that the 5.5 nm SnO<sub>x</sub> layer is totally oxidized into SnO<sub>2</sub> after exposure to the air. At  $d_{SnOx}$  = 8.5 nm, the Sn 3d spectra of the surface and etched layer were obtained, as illustrated in figure 3(b) and (c), respectively. In figure 3(b), it is manifested from the peak deconvolution that the SnO<sub>2</sub> phase is mixed with the SnO one (485.9 eV and 494.3 eV for  $\operatorname{Sn}^{2+3}\operatorname{d}_{5/2}$  and  $\operatorname{Sn}^{2+3}\operatorname{d}_{3/2}$ , respectively [16]). After etching, however, the spectrum only presents a spin-orbit doublet peak which can be assigned to SnO. Similar to the 8.5 nm case, the topmost surface layer of the 19 nm film is also consisted of SnO<sub>2</sub> and SnO mixed phases, but with more SnO content (Fig. 3(d)). After etching, the SnO and metallic Sn phases are present, as depicted in figure 3(e), where a spin-orbit doublet peak assigned to SnO with two small shoulders centered at 484.4 eV  $(Sn^0 3d_{5/2})$  and 492.8 eV  $(Sn^0 3d_{3/2})$  is clearly illustrated.

It is speculated that the negative shift of  $V_{\rm th}$  with increasing  $d_{SnOx}$  is related to the composition evolution of the  $SnO_x$  layers. The  $SnO_x$  film deposited by e-beam evaporation generally contains SnO and Sn species [15], and both of the species are good oxygen killers. In our case, the oxygen is coming from either air or the a-IGZO underlayer that has loosely bound oxygen [17]. When  $d_{SnOx}$  =5.5 nm, the ultrathin film might be oxidized into  $SnO_2$  quickly by the  $O_2$  and  $O_2$  in the air, and the oxygen provider coming from the a-IGZO

Fig. 3. The Sn 3d core level XPS spectra of SnO<sub>x</sub> capping layers with different thicknesses

underlayer cannot be ruled out of course. It's well known that the oxygen lose in oxide semiconductors would result in the increase of the electron concentration due to the increase of oxygen vacancies. As a result, the  $V_{\rm th}$  of 5.5 nm SnO<sub>x</sub> covered a-IGZO TFT is shifted negatively. The thicker of the SnO<sub>x</sub> film, the more easily of the loosely bound oxygen from a-IGZO getting access to oxidize the SnO and/or Sn spices in the inner sub-layer of SnO<sub>x</sub>, leading to more oxygen deficiencies and higher electron concentration in the channel layer. This speculation is matching well with the experimental results, i.e., the continuous negative-shift of  $V_{\rm th}$  with increasing  $d_{SnOx}$ .

One may suggest that the formation of the  $SnO_x/IGZO$  bilayer semiconductor structure could be another reason to account for the negative-shift of  $V_{th}$ , since  $SnO_x$  is a semiconductor. However, amorphous  $SnO_x$  films deposited by e-beam evaporation are of high resistance according to our previous reports [15]. It should be noted that the subsequently deposited ultra-thin  $SnO_x$  capping layer could not form good contact with the source and drain electrodes. So, the  $SnO_x$  film is believed to be an insulator capping layer rather than the back channel layer.

Interestingly, the field-effect mobility is generally improved with increasing  $d_{SnOx}$ , as manifested in Table 1. The negative shift of  $V_{th}$  along with the increased field effect mobility was also reported elsewhere [18], in which the usage of Ca/Al capping layer onto the back channel of a-IGZO TFT could eliminate the loosely bound oxygen species and in the a-IGZO channel. The removal of loosely bound oxygen in IGZO reduces the defect density, lowers the potential barrier above mobility edge, and then enhances electron mobility. [18]. For our case, the improved mobility and  $V_{th}$  negative shift were achieved with compromising the S.S factor, which is quite complicated and need further investigations.

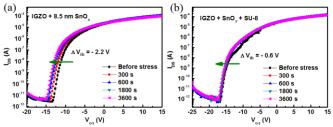

In order to improve the device stability, SU-8 resist was chosen to passivate the TFTs in this research. The bias stability of the TFTs with or without SU-8 was carried out. Figure 4 (a) and 4 (b) show the transfer curves of a typical TFT (with  $d_{SnOx}$  = 8.5 nm) as a function of bias stress duration. A negative shift of 2.2 V and 0.6 V after 3600 seconds bias stress was observed for the unpassivated and SU-8 passivated TFTs, respectively. The above comparison indicates that not SnO<sub>x</sub> layer but the SU-8 plays the passivation layer role to stabilize the device performance.

For the fabrication of the E/D inverter, the TFT with  $d_{SnOx}$  = 8.5 nm was chosen as the load, because of its better device

Fig. 4. (a) and (b) Transfer curves as a function of bias stress duration for the unpassivated and SU-8 passivated 8.5 nm  $SnO_x$ -capped a-IGZO TFTs. The bias stress conditions is  $V_G$ =5V.

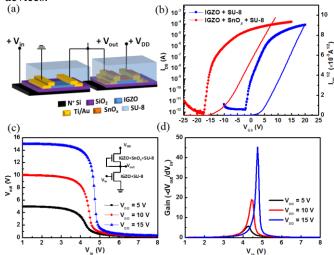

performance (sound field-effect mobility, steep S.S and huge  $V_{\text{th}}$  difference with respect to the  $SnO_x$  uncapped device). Figure 5(a) shows the block diagram of the fabricated inverter. The  $V_{th}$  of the driver (without SnO<sub>x</sub>) and load (8.5 nm SnO<sub>x</sub>-capped) TFTs is 4.0 V and -11.1 V, working in a depletion mode (D-mode) and an enhancement mode (E-mode) respectively, as manifested in figure 5(b). The voltage transfer curve (VTC) of the inverter was obtained at a supply voltage  $V_{\rm DD}$  of 5V, 10 V and 15 V. The VTC and the corresponding voltage gain are shown in figure 5(c) and 5(d). The inset of figure 5(c) is the equivalent circuit diagram of the logic inverter. The operation of the inverter can be described as, when V<sub>in</sub> is low (e.g.,  $V_{in} = 1$  V), the drive device would be at 'OFF' state while the load device working at 'ON' state. A low current flows through the load device, resulting in a minimal voltage drop across the load device. The above progress could account for the high output of the inverter (almost 15 V). On the contrary, if  $V_{in}$  is high (e.g.,  $V_{in} = 8 \text{ V}$ ), both of the two TFTs are at 'ON' state. A high current flows through the load device, leading to a low output (almost 0 V). The voltage gain of the inverter shown in figure 5(d) is about 5.9, 19.5 and 45.9 at  $V_{\rm DD}$ = 5, 10, 15 V, respectively, which is competitive with the previous report [19]. In addition, the fabrication process of this inverter is very similar to that of the conventional a-IGZO TFTs except for one additional capping step, opening up a way for the fabrication of low-cost and easy-fabrication microelectronic devices.

Fig. 5. (a) The device structure layout of the NMOS E/D inverter. (b) Transfer curves of 8.5nm SnO $_x$  capped and the uncapped IGZO TFT, and both TFTs were passivated by SU-8. (c) Voltage transfer curves of the inverter measured at supply voltage  $V_{\rm DD}$  of 5V, 10 V and 15 V (The inset shows the inverter circuit diagram). (d) Corresponding voltage gains ( $-dV_{\rm out}/dV_{\rm in}$ ) of the inverter.

### REFERENCES

- [1] J. F. Wager, B. Yeh, R. L. Hoffman, and D. A. Keszler, "An amorphous oxide semiconductor thin-film transistor route to oxide electronics," *Curr. Opin. Solid State Mater. Sci.*, vol. 18, no. 2, pp. 53-61, Apr. 2014. DOI: 10.1016/j.cossms.2013.07.002

- [2] M. Mativenga, M. H. Choi, J. W. Choi, and J. Jang, "Transparent Flexible Circuits Based on Amorphous-Indium-Gallium-Zinc-Oxide Thin-Film Transistors," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 170-172, Feb. 2011. DOI: 10.1109/LED.2010.2093504

- [3] W. T. Chen and H. W. Zan, "High-Performance Light-Erasable Memory and Real-Time Ultraviolet Detector Based on Unannealed Indium-Gallium-Zinc-Oxide Thin-Film Transistor," *IEEE Electron Device Lett.*, vol. 33, no. 1, pp. 77-79, Jan. 2012. DOI: 10.1109/LED.2011.2171316

- [4] S. C. Wu, H. T. Feng, M. J. Yu, I. T. Wang, and T. H. Hou, "Flexible Three-Bit-Per-Cell Resistive Switching Memory Using a-IGZO TFTs," *IEEE Electron Device Lett.*, vol. 34, no. 10, pp. 1265-1267, Oct. 2013. DOI: 10.1109/LED.2013.2278098

- [5] Y. C. Shen, C. H. Yang, S. W. Chen, S. H. Wu, T. L. Yang, and J. J. Huang, "IGZO thin film transistor biosensors functionalized with ZnO nanorods and antibodies," *Biosens. Bioelectron.*, vol. 54, pp. 306-310, Apr. 2014. DOI: 10.1016/j.bios.2013.10.043

- [6] Dhananjay, C. W. Chu, C. W. Ou, M. C. Wu, Z. Y. Ho, K. C. Ho, and S. W. Lee, "Complementary inverter circuits based on p-SnO<sub>2</sub> and n-In<sub>2</sub>O<sub>3</sub> thin film transistors," *Appl. Phys. Lett.*, vol. 92, no. 10, pp. 232103-1-232103-3, Jun. 2008. DOI: 10.1063/1.2936275

- [7] P. T. Liu, Y. T. Chou, L. F. Teng, and C. S. Fuh, "High-gain complementary inverter with InGaZnO/pentacene hybrid ambipolar thin film transistors," *Appl. Phys. Lett.*, vol. 97, no. 8, pp. 083505-1-083505-3, Aug. 2010. DOI: 10.1063/1.3483616

- [8] L. Y. Liang, H. T. Cao, X. B. Chen, Z. M. Liu, F. Zhuge, H. Luo, J. Li, Y. C. Lu, and W. Lu "Ambipolar inverters using SnO thin-film transistors with balanced electron and hole mobilities," *Appl. Phys. Lett.*, vol. 100, no. 26, pp. 263502-1-263502-4, Jun. 2012. DOI: 10.1063/1.4731271

- [9] J. M. Lee, I. T. Cho, J. H. Lee, and H. I. Kwon, "Full-Swing InGaZnO Thin Film Transistor Inverter with Depletion Load," *Jpn. J. Appl. Phys.*, vol. 48, no. 10, pp. 100202-1-100202-3, Oct. 2009. DOI: 10.1143/JJAP.48.100202

- [10] P. C. Debnath and S. Y. Lee, "Full swing logic inverter with amorphous SiInZnO and GaInZnO thin film transistors," *Appl. Phys. Lett.*, vol. 101, no. 9, pp. 092103- 092103-3, Aug. 2012. DOI: <u>10.1063/1.4747800</u>

- [11] I. T. Cho, J. W. Lee, J. M. Park, W. S. Cheong, C. S. Hwang, J. S. Kwak, I. H. Cho, H. I. Kwon, H. Shin, B. G. Park, and J. H. Lee, "Full-Swing a-IGZO Inverter With a Depletion Load Using Negative Bias Instability Under Light Illumination," *IEEE Electron Device Lett.*, vol. 33, no. 12, pp. 1726-1728, Dec. 2012. DOI: 10.1109/LED.2012.2221454

- [12] M. J. Seok, M. H. Choi, M. Mativenga, D. Geng, D. Y. Kim, and J. Jang, "A Full-Swing a-IGZO TFT-Based Inverter With a Top-Gate-Bias-Induced Depletion Load," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1089-1091, Aug. 2011. DOI: 10.1109/LED.2011.2157798

- [13] J. F. Wager, K. Hoshino, E. S. Sundholm, R. E. Presley, R. Ravichandran, C. C. Knutson, D. A. Keszler, R. L. Hoffman, D. A. Mourey, and J. Robertson, "A framework for assessing amorphous oxide semiconductor thin-film transistor passivation," *J. Soc. Inf. Disp.*, vol. 20, no. 10, pp. 589-595, Oct. 2012. DOI: 10.1002/jsid.120

- [14] E. Fortunato, P. Barquinha, and R. Martins, "Oxide semiconductor thin-film transistors: a review of recent advances," *Adv. Mater.*, vol. 24, no. 22, pp. 2945-2986, Jun. 2012. DOI: <u>10.1002/adma.201103228</u>

- [15] L. Y. Liang, Z. M. Liu, H. T. Cao, and X. Q. Pan, "Microstructural, Optical, and Electrical Properties of SnO Thin Films Prepared on Quartz via a Two-Step Method," ACS Appl. Mat. Interfaces, vol. 2, no. 4, pp. 1060-1065, Apr. 2010. DOI: 10.1021/am900838z

- [16] H. Luo, L. Y. Liang, H. T. Cao, Z. M. Liu, and F. Zhuge, "Structural, Chemical, Optical, and Electrical Evolution of SnO<sub>x</sub> Films Deposited by Reactive rf Magnetron Sputtering," *ACS Appl. Mat. Interfaces*, vol. 4, no. 10, pp. 5673-5677, Oct. 2012. DOI: 10.1021/am301601s

- [17] J. Y. Kwon and J. K. Jeong, "Recent progress in high performance and reliable n-type transition metal oxide-based thin film transistors," *Semicond. Sci. Technol.*, vol. 30, no. 2, pp. 024002-1- 024002-16, Feb. 2015. DOI: 10.1088/0268-1242/30/2/024002

- [18] H. W. Zan, C. C. Yeh, H. F. Meng, C. C. Tsai, and L. H. Chen, "Achieving High Field-Effect Mobility in Amorphous Indium-Gallium-Zinc Oxide by Capping a Strong Reduction Layer,"

- *Adv. Mater.*, vol. 24, no. 26, pp. 3509-3514, Jul. 2012. DOI: 10.1002/adma.201200683

- [19] H. W. Zan, W. T. Chen, C. C. Yeh, H. W. Hsueh, C. C. Tsai, and H. F. Meng, "Dual gate indium-gallium-zinc-oxide thin film transistor with an unisolated floating metal gate for threshold voltage modulation and mobility enhancement," *Appl. Phys. Lett.*, vol. 98, no. 15, pp. 153506-1-153506-3, Apr. 2011. DOI: 10.1063/1.3578403